## Quantum Circuit Discovery for Fault-Tolerant Logical State Preparation with Reinforcement Learning

Remmy Zen,<sup>1,\*</sup> Jan Olle,<sup>1</sup> Luis Colmenarez,<sup>2,3</sup> Matteo Puviani,<sup>1</sup> Markus Müller,<sup>2,3</sup> and Florian Marquardt<sup>1,4</sup>

Forschungszentrum Jülich, 52425 Jülich, Germany

The realization of large-scale quantum computers requires not only quantum error correction (QEC) but also fault-tolerant operations to handle errors that propagate into harmful errors. Recently, flag-based protocols have been introduced that use ancillary qubits to flag harmful errors. However, there is no clear recipe for finding a fault-tolerant quantum circuit with flag-based protocols, especially when we consider hardware constraints, such as qubit connectivity and available gate set. In this work, we propose and explore reinforcement learning (RL) to automatically discover compact and hardware-adapted fault-tolerant quantum circuits. We show that in the task of fault-tolerant logical state preparation, RL discovers circuits with fewer gates and ancillary qubits than published results without and with hardware constraints of up to 15 physical qubits. Furthermore, RL allows for straightforward exploration of different qubit connectivities and the use of transfer learning to accelerate the discovery. More generally, our work opens the door towards the use of RL for the discovery of fault-tolerant quantum circuits for addressing tasks beyond state preparation, including magic state preparation, logical gate synthesis, or syndrome measurement.

### I. INTRODUCTION

Quantum systems are highly fragile due to their susceptibility to errors caused by decoherence. Furthermore, quantum operations are imperfect and error-prone. Therefore, in order to harness quantum systems for computation, the error rates must be significantly reduced. Quantum error correction (QEC) is essential to protect quantum information from these errors, allowing us to perform complex and reliable computations [1, 2]. The basic idea behind QEC is to encode logical qubits into multiple noisy physical qubits in such a way that we can detect and correct errors without destroying the logical state. Although the implementation of QEC is a challenging task, recently we have seen several experimental breakthroughs of QEC with different quantum computing platforms [3–9], first quantum circuits carried out on up to 48 logical qubits [10, 11] and crossing the breakeven point of beneficial QEC [12–14].

QEC operations are often expressed using a sequence of quantum gates that forms a quantum circuit. However, these gates are faulty and multi-qubit gates proliferate the errors, compromising the scalability of QEC. In general, the more gates, the more errors are introduced, making QEC less effective [15–17]. Therefore, we want to minimize the number of possible faulty operations that can lead to harmful errors: this is achieved by designing fault-tolerant (FT) circuits [18]. In FT circuits, all faults (gates, measurements, errors, resets) that our QEC code cannot correct become less likely to occur below a specific threshold as the distance of the code increases (see

Sec. II C for more details). In consequence, only by using FT schemes we can ensure systematic improvement in correction as the size of the code scales. Therefore, FT is of paramount importance in making scalable quantum computers [2, 15–17]. Several classes of FT protocols have been proposed [6, 18–22]. Among the first ones was Shor-type error correction [23] which relies on additional GHZ states and repeated measurements to check for errors. Another scheme is Steane-type error correction, which uses additional logical qubits to detect errors [24– 26]. Both approaches suffer from a large qubit overhead. Recently, flag fault-tolerant error correction [20, 27–31] was introduced as a way to achieve fault-tolerant protocols with a minimal number of ancilla qubits, e.g. sometimes requiring only one extra qubit. For instance, in the specific case of preparing a state fault-tolerantly, a flag fault-tolerant protocol uses a verification circuit after the encoding circuit that utilizes a few extra ancilla qubits, known as flaq qubits, to flag harmful errors while keeping the logical state intact. There are already examples of flag verification circuits in state preparation on several QEC codes [32–36]. They have also been shown to be effective in reducing logical error rates in experimental realizations [3, 6, 7, 37–39].

Despite their success, flag-based protocols are typically handcrafted. Furthermore, flag-based protocols have so far been implemented in devices with all-to-all qubit connectivity. A transpilation process [40–42] can be applied to the circuit to respect the qubit connectivity and gate set, but it will generally make it non-FT. In other words, the automatic compilation [43–47] of FT circuits has not been widely explored yet.

In this work, we present a novel approach based on reinforcement learning (RL) to automatically discover

<sup>&</sup>lt;sup>1</sup>Max Planck Institute for the Science of Light, Staudtstraße 2, 91058 Erlangen, Germany <sup>2</sup>Institute for Quantum Information, RWTH Aachen University, 52056 Aachen, Germany

<sup>&</sup>lt;sup>3</sup>Peter Grünberg Institute, Theoretical Nanoelectronics,

<sup>&</sup>lt;sup>4</sup> Department of Physics, Friedrich-Alexander Universität Erlangen-Nürnberg, Staudtstraße 5, 91058 Erlangen, Germany (Dated: May 20, 2024)

<sup>\*</sup> remmy.zen@mpl.mpg.de

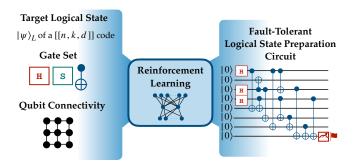

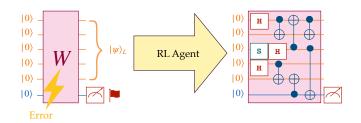

FIG. 1. Discovery of fault-tolerant logical state preparation circuit with reinforcement learning (RL). Given the target logical state  $|\psi\rangle_L$  of a specified [[n,k,d]] code, a gate set, and a qubit connectivity, we use RL to automatically discover circuits for preparing  $|\psi\rangle_L$  fault-tolerantly with flag qubits.

fault-tolerant quantum circuits for QEC. RL is an approach in which an agent learns to make decisions by interacting with an environment in order to maximize its reward through guided trial and error. We apply our method to the task of logical state preparation. Specifically, our approach is based on the automatic discovery of quantum circuits that fault-tolerantly prepare the logical states of a given QEC code under hardware constraints. That is, we can constrain the qubit connectivity and the gate set based on the quantum platforms of interest, as shown in Fig. 1. The RL agent needs to find an optimal strategy by applying a discrete gate at each step, guided by reward signals.

Recently, reinforcement learning (RL) [48] has emerged as a useful tool for solving various problems in quantum technologies [49]. It has been applied to quantum error correction [50–55], quantum control and state preparation [56–61], and quantum compilation [62–68] among many others. It has been shown that RL stands out in quantum state preparation when the gates applied by the agent are discrete [56]. Furthermore, RL is suitable for our task because it can be formulated as a goal-oriented task that is specified in the reward signals. In addition, we find that RL is capable of efficiently navigating large and complex quantum circuit spaces. Finally, RL enables efficient and flexible automated discovery through transfer learning, i.e., reusing trained RL agents for similar but different quantum circuit problem instances. This is not possible, for example, in the method proposed in Ref. [69], where finding a fault-tolerant quantum circuit is framed as a Satisfiability Modulo Theory (SMT) problem.

We test our method on several QEC codes, including the 5-qubit perfect code, the 7-qubit Steane code, the 9-qubit Shor code, and the 15-qubit Reed-Muller code. Our first RL approach is to separate the task of finding a FT logical qubit encoding protocol into a logical state preparation task followed by a verification circuit synthesis task. Individually, the RL method for each task already produces quantum circuits that have better or similar performance to existing circuits. More interest-

ingly, by integrating the logical state preparation and verification circuit synthesis tasks, a single RL agent can directly prepare FT logical states and is able to outperform all other available approaches. Thus, this work establishes RL as a viable approach for FT quantum circuit synthesis tasks that go beyond the preparation of logical states.

The paper is organized as follows. In Sec. II, we give a brief background on FT QEC and RL. In Sec. III, we describe our general reinforcement learning framework for fault-tolerant logical state preparation. The preparation of a FT logical state can be divided into two successive tasks: the preparation of the logical state, described in Sec. IV, followed by the synthesis of the verification circuit, described in Sec. V. In Sec. VI, we go beyond the separation of tasks and present our main integrated approach, where we directly prepare FT logical states. In Sec. VII we summarize our work and discuss further extensions.

### II. BACKGROUND

### A. Quantum Error Correction

Here, we briefly review basic concepts from stabilizer quantum error correcting (QEC) codes and introduce the notation that will be used in this paper. Readers familiar with these concepts are invited to skip to Sec. II B.

The main idea of quantum error correction is to introduce redundancy by encoding k logical qubits into n > knoisy physical gubits. In this work, we focus on a specific type of QEC codes called  $stabilizer\ codes\ [70]$ . Given the Pauli group of n qubits, the set of stabilizers S is a subgroup such that all elements of S commute with each other and  $-I \notin S$ . If S is generated by the set  $G = \langle g_1, \dots, g_{n-k} \rangle$ , then the code space corresponds to the joint +1 subspace of all generators  $g_i$ , hosting logical quantum states  $|\psi\rangle$ , for which  $g_i|\psi\rangle = |\psi\rangle$  for all generators. Within the code space, each code word can be transformed into one another using the logical operators  $Z_L^i, X_L^i$ , with i = 1, ..., k, where  $Z_L^i$  and  $X_L^i$  commute with all elements of the stabilizer group and satisfy  $[Z_L^i, X_L^j] = 2Z_L^i X_L^j \delta_{ij}$ , where  $\delta_{ij}$  is the Kronecker delta. For instance, for the case of a QEC code hosting a single logical qubit,  $k=1, Z_L^1|0\rangle_L=|0\rangle_L, Z_L^1|1\rangle_L=-|1\rangle_L$  and  $X_L^1|0\rangle_L=|1\rangle_L$ . Thus, once S is chosen, the choice of logical operators fixes the codewords  $|0\rangle_L$  and  $|1\rangle_L$  and all their linear combinations.

The weight of a Pauli operator is the number of non-identity components within that operator. The minimum weight among all possible choices of logical operators defines the distance d of the QEC code. A QEC code is able to detect d-1 errors and correct  $\lfloor (d-1)/2 \rfloor$  errors. A distance d QEC code encoding k logical qubits into n physical qubits is denoted as [[n,k,d]].

A QEC code can be defined solely by its stabilizer generators  $g_i$ . When the stabilizer generators consist of eigenvalues  $g_i$ .

ther X or Z Pauli matrices, such that they can be related to two independent classical codes  $C_X$  and  $C_Z$  for the X and Z stabilizers, they are called Calderbank-Shor-Steane (CSS) codes [71, 72]. Due to their simplicity and connection to classical codes, CSS codes are at the frontier of theoretical and practical implementations of QEC [3, 13, 37]. Two famous examples of CSS codes are the surface/toric code [17, 73] and the color code [74, 75]. In our work we consider the search for FT and non-FT encoding circuits for several CSS codes (including color codes) and the 5-qubit code, which is a non-CSS code (see Appendix F for the code definitions).

## B. Logical Qubit Encoding Circuit

Once a QEC code and the logical operators are chosen, the next step is to find a way to encode the desired logical states. For stabilizer codes, one approach is to measure the stabilizers and apply conditional local operations that bring the state back into the code space [5, 7]. This approach relies on stabilizer measurements, which has the disadvantage of being susceptible to measurement errors, and forces repeated measurements according to the code distance to ensure FT, resulting in a large gate count. An alternative approach is to find a unitary circuit U that encodes such information using the given code [3, 4, 6, 37]. For instance, encoding a logical zero  $|0\rangle_L$  implies finding a circuit that performs the task  $|0\rangle_L = U|0\rangle^{\otimes n}$ . Unlike stabilizer measurement encodings, unitary encodings avoid repeated stabilizer measurements, potentially reducing the number of gates. Importantly, even after choosing a QEC code and codeword, there is no unique recipe for finding an encoding unitary U.

NISQ devices often have specific constraints, such as limited qubit connectivity and native gate set availability. To fulfill these constraints, a transpilation process is commonly applied to the circuit. The whole procedure typically involves mapping the qubits in the circuit to physical qubits, routing the qubits based on the connectivity by inserting swap gates, decomposing gates into native gates, and optimizing the final circuit [40–42]. Since the procedure involves inserting and decomposing gates, this process will, in general, increase the size of the circuit.

Due to their simplicity and relevance, we restrict ourselves to logical Pauli eigenstates only. Thus, we can focus only on Clifford circuits, where the logical state  $|\psi\rangle = U|0\rangle^{\otimes n}$  is always determined by its stabilizer tableau [76]. In particular, a tableau of a single logical codeword contains the n-k stabilizer generators and the k logical operators, which can be represented as a binary matrix that scales quadratically with respect to n. Appendix A shows more details on the tableau representation. While different tableaus may represent the same state, their canonical form [70] remains the same. A canonical tableau can be obtained by applying Gaussian elimination to the tableau [76]. This means that differ-

ent encoding circuits preparing the same logical state will have the same representation. We will use this representation later as an input to the RL agent. The canonical representation helps the RL agent to learn more effectively and efficiently by reducing complexity and ensuring consistency of the input space.

It has been proven that Clifford circuits can be efficiently simulated using classical computers [76]. Despite its simplicity, finding a compact circuit is still not trivial [77, 78]. Several methods have been proposed to prepare arbitrary stabilizer states [76, 79–82]. Some methods have also been developed specifically for the preparation of logical states of stabilizer QEC codes [83–87]. However, these techniques generally do not include any hardware constraints, nor do they output fault-tolerant quantum circuits, the latter of which we will focus on next.

#### C. Fault-Tolerant State Preparation

In practice, quantum gates are faulty and thus introduce errors in state preparation. A simple but effective model for gate failures is to consider the perfect gate to be applied only with probability 1-p, where p is the probability that a fault occurs when the gate is applied. In this work, we consider any fault consisting of bit flips (X Pauli), phase flips (Z Pauli), or both (Y Pauli). Therefore, single qubit gates have 3 error generators  $\mathcal{E} = \{\sigma_k\}/I$  and two qubit gates have 15 error generators  $\mathcal{E} = \{\sigma_k\}/I$  and two qubit gates have 15 error generators  $\mathcal{E} = \{\sigma_k\}/I$  and two qubit gates have 15 error generators the Pauli matrices including the identity. More formally, the errors introduced by the gates are modeled by introducing a depolarizing channel after the gates:

$$G\rho G^{\dagger} = (1-p)G\rho G^{\dagger} + \sum_{E \in \mathcal{E}} \frac{p}{|\mathcal{E}|} EG\rho G^{\dagger} E,$$

(1)

where G is the ideal gate, p is the probability of having a gate error, and  $|\mathcal{E}|$  is the number of elements in the set of all error generators  $\mathcal{E}$ . This is the standard modeling of gate errors, often referred to as *circuit-level noise* [3, 6, 8, 84].

An error E can be propagated through the circuit in such a way that a unitary  $U_E = \tilde{E}U$  can always be written as the error-free U followed by the propagated error  $\tilde{E}$ . For Clifford unitaries,  $\tilde{E}$  remains a single Pauli error obtained by propagating E through the individual gates one by one [84]. There are two classes of errors that we consider according to their propagated version: (i)  $\tilde{E}$  is a member of the stabilizer group, thus acting trivially on the stabilizer states, or its weight is small enough that it can be removed by QEC, in which case, we say the error is tolerable. (ii) Its weight is large enough that it cannot be corrected, causing a logical failure after a QEC cycle. We call such errors harmful.

In practice, any circuit that is not carefully designed will have components whose failures lead to harmful errors. For example, even a single gate failure with probability p can lead to a logical error. Therefore, increasing the code distance of the QEC code would not suppress the logical error rate, because there would always be uncorrectable events with probability p. Formally, for a code of distance d able to correct errors of weight  $t = \lfloor (d-1)/2 \rfloor$ , the logical error rate in a FT architecture  $p_L$  scales as  $p_L \sim p^{t+1}$  for p below the threshold [15, 16, 23], which ensures an ever decreasing logical error rate when increasing the size (number of physical qubits) of the QEC code. In contrast, if a harmful error occurs with probability p, the expected gain from QEC is lost, no matter how large d is. In other words, all error events with probability  $p^{\alpha}$ ,  $\alpha < (d+1)/2$  should be tolerable in the sense that they are corrected after QEC cycles. A circuit or component that fulfills the latter condition is called fault-tolerant (FT) [20, 21, 28, 29, 69, 88–91]. As an example, let us consider a code with d=3 that corrects any single qubit error. Some gate failures in this code can produce weight-two harmful errors. Therefore,  $p_L \sim p$  if the circuit design is non-FT. If the encoding circuit is made fault-tolerant, then all errors coming from a single gate failure become tolerable, and only errors coming from two gate failures are harmful, hence  $p_L \sim p^2$ .

There is no unique way to render a circuit FT [3, 21, 28, 69, 89, 92, 93]. Recently, flag verification circuits [20, 28, 29] have been proposed for turning non-FT circuits into FT ones. The flag verification procedure is based on coupling additional ancilla flag qubits to the main register in such a way that the error-free state is unperturbed and the flag qubit(s) always have the same measurement outcome. When faults that lead to harmful errors occur in any component of the circuit, the flag qubit(s) are triggered, i.e., flip the measurement outcome of the flag ancilla qubit(s). Thus, harmful errors are flagged out by the flag qubit, allowing us to do postselection on the ancilla measurement outcomes. One can then apply a repeat-until-success mechanism (rejecting outcomes with triggered flag qubits and accepting outcomes without triggered flag qubits) and apply QEC to remove the tolerable errors.

### D. Reinforcement Learning

Reinforcement learning (RL) [48] aims to train an agent to take an optimal set of actions in an environment (here a simulation of our physical system). This goal is achieved by maximizing the expected returns or the cumulative rewards via a guided trial-and-error approach. In this work, we focus on model-free reinforcement learning, where the agent does not know about the model of the environment. Formally, an RL agent observes the state of the RL environment  $s_t$ , applies a discrete action  $a_t$  at time step t that changes the state of the environment from  $s_t$  to  $s_{t+1}$ , and receives an instantaneous reward  $r_t$ . An episode is a trajectory of states and actions  $\tau = (s_0, a_0, s_1, a_1, \ldots, s_T)$  from the initial state  $s_0$  to the

terminal state  $s_T$ . An RL agent learns a policy function  $\pi_{\theta}$  parameterized by  $\theta$ , which maps each state of the environment to a probability distribution over all possible actions.  $\pi_{\theta}(a_t|s_t)$  gives the probability of applying action  $a_t$  for a given state  $s_t$  of the environment. The RL agent is trained to maximize the expected returns (cumulative reward) over multiple episodes  $\mathcal{J}(\theta) = \mathbb{E}_{\tau \sim \pi_{\theta}}[\sum_{t=0}^{T} r_t]$ . Policy gradient methods [94] optimize the objective

function  $\mathcal{J}(\theta)$  with gradient ascent. In this work, we use a deep reinforcement learning algorithm where a deep neural network is used to compute  $\pi_{\theta}$ , where  $\theta$  corresponds to the weights and biases of a neural network. We use a state-of-the-art variant of policy gradient methods called Proximal Policy Optimization (PPO) [95]. In PPO, we use two networks: an actor and a critic network. The former determines the action taken by the agent, while the latter measures the quality of the action taken by the agent. Both networks take the representation of the observation as input. The actor network outputs the probability of taking each discrete action, while the value network outputs a value that corresponds to the expectation value of the cumulative reward. During training, the parameter  $\theta$  of the networks is updated in such a way that the objective is satisfied.

## III. REINFORCEMENT LEARNING FRAMEWORK FOR QUANTUM CIRCUIT DISCOVERY

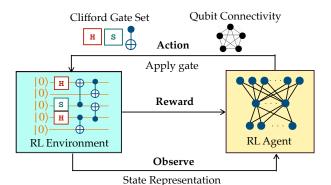

FIG. 2. The general RL framework in this work. The circuit is the environment, where its state is represented by its stabilizer canonical tableau. At each step, the RL agent observes the environment and applies a discrete Clifford gate as an action from the specified available gate set (e.g., the Hadamard gate H, the phase gate S, and the CNOT gate), taking into account qubit connectivity constraints. Subsequently, the agent receives a reward depending on the given task and the quality of the proposed circuit.

Here we first introduce the general RL framework as shown in Fig. 2. In this work, an RL agent is trained to output circuits (suggesting a sequence of gates) for a given task (i.e. logical state preparation, verification circuit synthesis, or integrated fault-tolerant logical state

preparation). At each step, the RL agent observes the state of a quantum circuit and applies a discrete Clifford gate to the quantum circuit as an action. A trajectory stops when the number of gates is greater than a preset maximum number (counting as a failure) or when it reaches the success criteria defined by the task. We assume that all physical qubits in the circuit are initialized in the  $|0\rangle$  state. The hardware constraints, such as the set of available Clifford gates and the qubit connectivity of the device considered, determine the set of possible actions that the agent can take. The reward is then given according to how well the quantum circuit proposed by the agent fulfills the task, which will be explained in the following sections.

We must then choose a representation of the RL agent's observation. The most common representation is to directly observe the quantum circuit [96, 97] or to observe the state vector of the state that the circuit represents [56, 58, 59, 98]. However, multiple quantum circuits could represent the same state, and the state vector representation scales exponentially with n. Since we are focusing on stabilizer codes, we can use the stabilizer tableau of the circuit as a representation of the state of the environment. Even better, we can use the canonical tableau as the representation, so that different circuits producing the same output state have the same representation. This representation scales quadratically with n.

Although the state representation is polynomial in n, a brute-force search of the circuit scales exponentially with the number of gates L. Suppose we choose a gate set consisting of  $G_1$  one-qubit gates and  $G_2$  two-qubit gates with all-to-all qubit connectivity. At each step, the agent must decide over  $nG_1+(n^2-n)G_2$  possible actions, which scales quadratically with n. Furthermore, if we assume that a circuit has L gates, then the space of all possible solutions grows exponentially as  $(nG_1+(n^2-n)G_2)^L$ , making search algorithms infeasible.

As a side note, instead of using a discrete Clifford gate set, one can also use a continuous gate set with a parameterized circuit and use a variational approach as in Ref. [99]. However, in a variational approach, the state can no longer be efficiently described within the stabilizer formalism. Furthermore, one has to design an ansatz and optimize the parameters, which generally does not scale well due to barren plateaus [100].

We use the PureJaxrL library [101] for the implementation of the PPO algorithm, which is written with the Jax [102] library to allow very fast parallel training on a GPU. We then implement the environment for each task using Jax. This means that the simulation of the Clifford circuits and the computation of the rewards run very fast in parallel on the GPU. Therefore, we train multiple agents in parallel and each agent is trained on multiple environments also in parallel. The code is available online [103]. The details of the hyperparameters used and the training process are described in Appendix B.

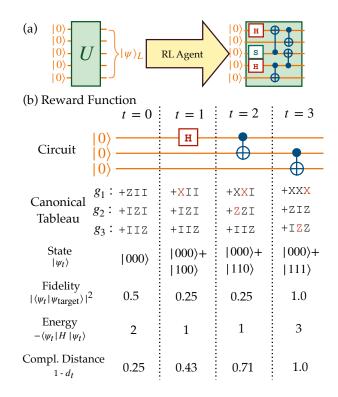

FIG. 3. Description and reward function for the logical state preparation task. (a) The logical state preparation task outputs a circuit U that prepares a target logical state  $|\psi\rangle_L$  of a [[n,k,d]] code. (b) The preparation of the state  $|\psi_{\rm target}\rangle = |000\rangle + |111\rangle$  (normalization factors are not shown for simplicity) from the initial state  $|\psi_0\rangle = |000\rangle$ . We show the value of the three possible functions at each time step t for the reward: fidelity  $|\langle \psi_t | \psi_{\rm target} \rangle|^2$ , energy  $\sum_i \langle \psi_t | H | \psi_t \rangle$  used in [99], and our proposed complementary tableau distance  $1-d_t$ . In this case, the proposed complementary tableau distance is monotonically increasing, which is easier for RL algorithms to learn compared to the other functions.

### IV. LOGICAL STATE PREPARATION

### A. Task Description and Reward Function

The goal of the logical state preparation task is to find a circuit U that prepares the target stabilizer state (see Fig. 3(a)). The task requirement is the canonical tableau  $T_{\rm target}$  of the target stabilizer state  $|\psi_{\rm target}\rangle$ . Note that although in this paper we focus on preparing logical states of a stabilizer code, this task is general enough to prepare any stabilizer state.

In any RL application, it is of utmost importance to design a good reward function according to the goal. A natural choice of the reward function is the *fidelity* of the state [56, 57, 59, 98, 104, 105]. For a given state at time step t,  $|\psi_{\rm t}\rangle$ , the fidelity can be computed as  $|\langle \psi_{\rm t}|\psi_{\rm target}\rangle|^2$ , however it suffers from the sparse reward problem [48]. As an illustration, consider preparing  $|\psi_{\rm target}\rangle=|111\rangle$  from an initial state of  $|\psi_0\rangle=|000\rangle$ . The agent would have to apply the Pauli X gate to every qubit

that changes the state from  $|000\rangle$  to  $|100\rangle$  to  $|110\rangle$  to  $|111\rangle$ . However, the fidelity value only changes on the last step, since  $|\langle 000|111\rangle|^2 = |\langle 100|111\rangle|^2 = |\langle 110|111\rangle|^2 = 0$ . This makes the RL agent harder to train because it does not get immediate feedback.

Since we are preparing a stabilizer state, there are seemingly better rewards that we can use, but there are still drawbacks. In Ref. [99], finding a logical state of a stabilizer code is framed as finding the ground state of a Hamiltonian  $H = -\sum_{i=1}^{n-k} g_i - \sum_{j=1}^k O_L^j$ , where g are the generators of the target state and  $O_L$  are the logical operators. This then allows one to compute the energy as  $E = \sum_i \langle \psi_t | H | \psi_t \rangle$ . If  $|\psi_t\rangle = |\psi_{\text{target}}\rangle$ , then the ground state energy  $E_0 = -n$ . Ref. [99] used E as a cost function for the variational optimization of a parameterized circuit. In our case, we use -E instead, since we want to maximize the cumulative reward. Although the computation of this function scales linearly with n, it still suffers from the sparse reward problem. One can see that there are only 2n possible discrete energy values ranging from -n to n.

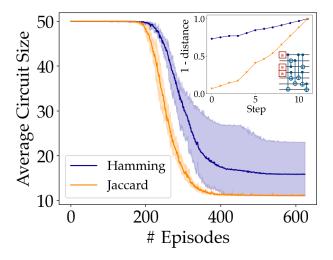

We introduce another measure that does not suffer from the sparse reward problem, and the computation of its value does not scale exponentially. We refer to it as the tableau distance  $d_{\rm t}$ , which is the distance between the tableau describing the output state of the currently proposed quantum circuit and the tableau of the target state. We convert the tableaus into binary vectors and measure the binary distance  $d_{\rm t}$  between the two. Here, we use the Jaccard distance (see discussion in Appendix C). We normalize the  $d_{\rm t}$  so that it ranges from 0 to 1 and we use the complementary tableau distance  $1-d_{\rm t}$  since the training of RL maximizes the cumulative reward.

Fig. 3(b) illustrates how the three possible functions (fidelity, energy, and complementary tableau distance) for the reward change for preparing  $|000\rangle + |111\rangle$  (normalization factors are not shown for simplicity) from  $|000\rangle$ . We see that in this case, unlike the other functions, the proposed complementary tableau distance  $1 - d_t$  always increases when gates are applied, giving good feedback to the RL agent. We can also see that from t=1 to t=2, applying the correct gate does not change the fidelity and energy functions, which is not a good feedback to the RL agent. This is not the case for  $1-d_t$ . Our empirical numerical experiments also showed that using our proposed complementary tableau distance function as a reward leads to faster convergence of the training of the RL agent compared to using the rewards based on the fidelity and the energy.

Finally, one can give the reward only at the last time step (e.g.  $r_t = 1 - d_L$  at t = L, otherwise  $r_t = 0$ ). However, this means that the agent does not receive immediate feedback after performing an action. Instead, we use the reward shaping technique [48] by giving a small intermediate value at each step so that the training converges faster. Therefore, at each time step t, we give the difference of the complementary tableau distance between t

and t-1, or more formally,

$$r_t = d_{t-1} - d_t. \tag{2}$$

In this case, the cumulative reward  $\sum_{t=0}^{L} r_t$  is still  $1-d_L$ . A trajectory stops when the complementary tableau distance is greater than a threshold  $\epsilon$  close to 1 (success) or the number of gates is greater than a threshold L (failure).

As a side note, one might notice that the reward function does not have a term that minimizes the number of gates. This is intrinsically embedded in the RL formulation, which we explain in more detail in Appendix E. Additionally, it is straightforward to extend the reward function to consider different objectives or constraints. For example, to minimize the number of two-qubit gates, we could add a term that gives a higher cost for two-qubit gates than for single-qubit gates.

### B. Results

We apply our approach to prepare logical states of different QEC codes. Our goal is not only to demonstrate the generality of our approach by benchmarking it as broadly as possible but also to address the ongoing and timely challenge of identifying optimized circuits. We are interested in the preparation of logical states of the following QEC codes. The first code that we consider is the smallest complete error-correcting code, the [[5, 1, 3]] perfect code [106], which has been realized experimentally, for example in [6, 7]. This code is non-CSS. We then consider several CSS codes. The first quantum error correction code, the [9, 1, 3] Shor code [107], which has been realized experimentally, for example in [108, 109]. We also consider 2D and 3D color codes [74, 75]. The [[7, 1, 3]]Steane code [71] is the smallest CSS and triangular 2D color code that has been realized experimentally, for example in [3, 6, 37, 110, 111]. We also explore the distance 5 2D color code, which is the [[17, 1, 5]] code [75]. Finally, we consider the smallest error-correcting 3D color code, the [[15, 1, 3]] Reed-Muller code [74, 112]. The stabilizer generators of these codes are listed in Appendix F for completeness.

In all of the codes mentioned above, we can choose  $Z^{\otimes n}$  as the logical  $Z_L$  operator. This means that we prepare the  $|0\rangle_L$  states of these codes, except for the [[9,1,3]] Shor code, where the same choice corresponds to the  $|+\rangle_L$  state. The preparation of other logical states can be achieved by changing the target logical operator accordingly. As an evaluation metric, we measure the circuit size, which corresponds to the number of gates in the circuit.

We first discuss the preparation of logical states on a device with all-to-all qubit connectivity and a gate set consisting of the gates H, S, and CNOT, which we refer to as the *standard gate set*. This connectivity and gate set is realistic, for example, in trapped-ion-based quantum computers [117].

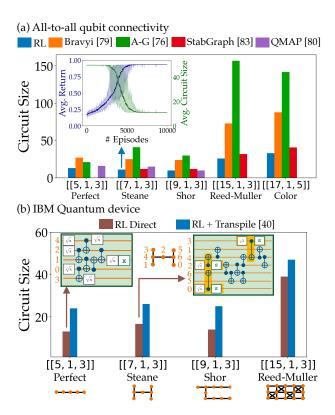

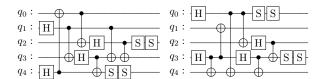

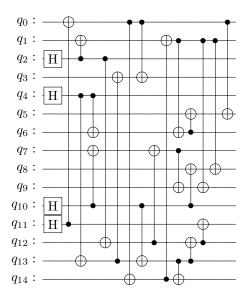

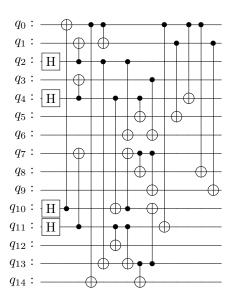

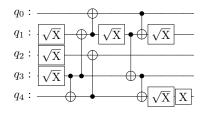

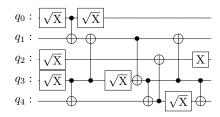

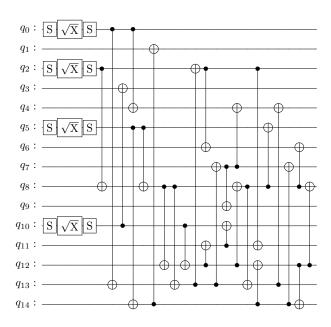

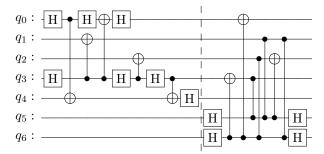

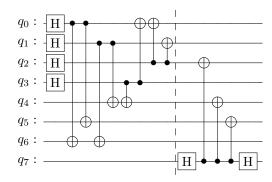

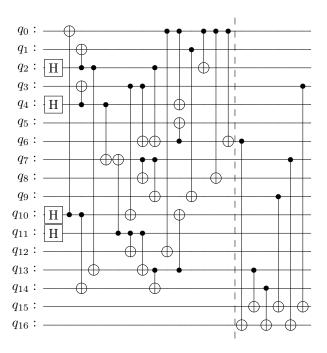

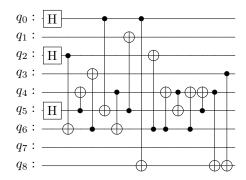

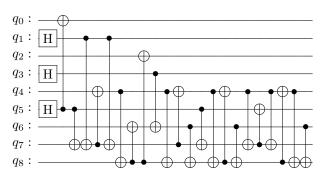

FIG. 4. Results for the logical state preparation task. (a) The minimum circuit size of different methods for logical state preparation of different QEC codes with all-to-all qubit connectivity and H, S, and CNOT gates. StabGraph [83] does not work for non-CSS codes such as the [[5, 1, 3]] perfect code. QMAP [80] could not prepare the state of the [[15, 1, 3]] and the [[17, 1, 5]] code in the allotted maximum time of 12 hours. The inset shows an example of the training progress for preparing the  $|0\rangle_L$  state of the [[7, 1, 3]] Steane code. (b) Comparison of circuit size from an RL agent that includes the connectivity and gate set during training (RL Direct) with respect to RL-prepared circuits for all-to-all qubit connectivity that have been transpiled with QISKIT [40] (RL + Transpile). Results shown for various IBM Quantum device connectivities [113–116] using CNOT,  $\sqrt{X}$ , X, and  $S = R_z(\pi/2)$  gates. The inset shows examples of RL-prepared circuits for the  $|0\rangle_L$ state of the [[5, 1, 3]] perfect and the [[7, 1, 3]] Steane code.

We compare our RL method with four different Clifford circuit synthesis methods, where one provides the tableau and the respective methods automatically synthesize a Clifford circuit. Two of them are available in the QISKIT [118] library, based on the algorithm provided by Bravyi et al. [79] and Aaronson-Gottesman [76]. We also compare with StabGraph [83], which works only for CSS codes and uses graph states, and QMAP [80], which converts the problem into a Boolean satisfiability (SAT) problem and solves it with a SAT solver. For QMAP, we use the MAX-SAT algorithm, use the depth as the optimization target, and then minimize the number of gates. We find that using the number of gates as the optimization target of the MAX-SAT algorithm is very slow even for small n.

Fig. 4(a) shows the comparison of the smallest circuit size between different methods for preparing logical states of different codes. We see that the RL method always prepared a smaller circuit size compared to the other methods. StabGraph [83] is specialized in preparing logical states of CSS codes, therefore it does not work for the [[5, 1, 3]] perfect code. QMAP [80] also did not finish the logical state preparation for n > 10 in the allotted maximum time of 12 hours. The inset of Fig. 4(a) shows the training progress for the preparation of the  $|0\rangle_L$  for the [[7, 1, 3]] Steane code. The shaded area indicates the minimum and maximum values over 10 agents trained in parallel, where each agent saw 16 environments in parallel. The entire training takes approximately 100 seconds on a single NVIDIA Quadro RTX 6000 GPU and produces 10 circuits. On average, the 10 agents converge after seeing about 6000 episodes. In Appendix G, we show some examples of circuits prepared by the RL agent and discuss some of the strategies that the RL agent learned. For example, we see that in some cases the agent would first try to get the correct tableau without worrying about the sign, and then uses Z gates (two S gates) to fix the sign.

So far, the agent is used only once after training to generate circuits for a specific logical state. However, an advantage of the deep RL method is that one can reuse the agent trained for one task and retrain it for another task. This is commonly referred to as transfer learning [119, 120]. For example, one can take the agent that prepares the  $|0\rangle_L$  state and reuse it to train another agent that prepares the  $|+\rangle_L$  state and the  $|+i\rangle_L$  state more efficiently. We show these results in Appendix H.

We now show that the RL method is robust enough to adapt to different realistic qubit connectivities and gate sets from different hardware platforms by constraining the actions that the RL agent can take. We illustrate this by focusing on several IBM Quantum devices. The IBM Quantum devices have CNOT, X,  $\sqrt{X}$ , and  $R_Z$  gates (parameterized rotation along the z-axis) as their native gate set. Instead of using an arbitrary  $R_Z$  gate, we choose to include the S gate, which can be translated into a  $R_Z(\pi/2)$  gate.

We prepare the  $|0\rangle_L$  state of the [[5,1,3]] perfect code on the IBMQ Manila [113] connectivity, the  $|0\rangle_L$  state of the [[7,1,3]] Steane code on the IBMQ Jakarta [114] connectivity, the  $|+\rangle_L$  state of the [[9,1,3]] Shor code on the IBMQ Guadalupe [115] connectivity, and the  $|0\rangle_L$  state of the [[15,1,3]] quantum Reed-Muller code on the IBMQ Tokyo [116] connectivity. These connectivities are shown at the bottom of Fig. 4(b). We trained several agents and take the circuit with the minimum circuit size.

We refer to the RL method that directly restricts the connectivity and gate set in the training as RL Direct. We compare it to the RL + Transpile method, where we take the RL-prepared circuit for all-to-all qubit connectivity and transpile it with the QISKIT transpiler [40]. Fig. 4(b) shows the comparison of circuit size between the

two methods. We see that circuits from the RL Direct method always have a smaller circuit size as compared to circuits obtained with the RL + Transpile method. This shows that restricting the actions of the RL agent based on the hardware constraint during the training is better than transpiling a circuit from all-to-all qubit connectivity.

The inset of Fig. 4(b) shows examples of a circuit prepared by the RL agent for the  $|0\rangle_L$  of the [[5,1,3]] perfect code on the IBMQ Manila connectivity and the [[7,1,3]] code on the IBMQ Jakarta connectivity. Interestingly, we see that in the circuit for the [[7,1,3]] code, the agent learns a new gate sequence  $\sqrt{X}$ , CNOT, and S (shaded in yellow in the figure). This gate sequence is equivalent to a H gate followed by a CNOT gate. The agent discovers this gate sequence because the H gate is not available as a native gate on IBMQ devices. Appendix I shows more examples of logical state preparation circuits on IBMQ devices

In terms of efficiency, the training of the RL agent to prepare the  $|0\rangle_L$  of the [[7,1,3]] Steane code for the IBMQ Jakarta connectivity takes approximately 200 seconds on a single NVIDIA Quadro RTX 6000 GPU. One could argue that this is much slower than transpiling a circuit for all-to-all qubit connectivity. However, as we have shown, the resulting circuit size is smaller and the training only needs to be done once. Furthermore, the training can be accelerated through transfer learning. In Appendix J, we show a technique where the agent trained to prepare a logical state for all-to-all qubit connectivity can be reused and retrained to prepare the same state with different connectivity.

In summary, we have shown that RL can prepare logical states of different QEC codes with smaller circuit sizes than other methods in all-to-all qubit connectivity. We also show that by directly incorporating the hardware constraint by restricting the connectivity and gate set in the training is better than transpiling a circuit for all-to-all qubit connectivity. Furthermore, we can reuse a trained RL agent to speed up the training of the RL agent for different but similar problems.

## V. VERIFICATION CIRCUIT SYNTHESIS

### A. Task Description and Reward Function

The goal of the verification circuit synthesis task is to synthesize a circuit V and use the ancilla flag qubits to flag harmful errors and thereby render the encoding protocol fault-tolerant (see Fig. 5). The task requirement is the sequence of gates that form the circuit U to prepare the target logical state  $|\psi\rangle_L$  and the number of the ancilla flag qubits  $n_A$ . It is possible that several circuits represent the same unitary U, but the propagated error would be different. The ancilla flag qubits are initialized in state  $|0\rangle$  and are always placed last in the qubit ordering. For a given circuit, it is usually not known a priori

FIG. 5. The verification circuit synthesis task prepares a circuit V that uses flag qubits to flag harmful errors, thereby rendering a state preparation fault-tolerant.

how many ancilla qubits are needed to flag all of the harmful errors. Therefore, it is possible that the agent cannot find a solution for a given number of ancillas. On the other hand, it is also possible that the agent will not use some ancillas if  $n_A$  is larger than needed.

There are underlying principles for designing FT flag verification circuits [20, 28], although they do not provide a direct recipe for FT circuit design. For instance, in the case of d=3 CSS codes, state verification is equivalent to measuring some logical operators [32]. However, for higher distances or non-CSS codes, a straight-up measurement of one of the logical operators does not necessarily lead to an FT verification. Our goal is to use reinforcement learning to automatically find verification circuits under very general constraints.

We consider three criteria that must be met for this task. The first and most important criterion is to ensure that all harmful errors are flagged. While applying gates to the ancilla, it is possible that the state will change. Therefore, preserving the logical state is the second criterion. Finally, we do not want that the data (non-ancilla) qubits are entangled with the flag qubits, since this will destroy the logical state when we measure the flag. Thus, the third criterion is that the final state is a separable or product state of the data qubits and the flag qubits such that  $VU|00...0\rangle = |\psi\rangle_L|\phi\rangle_F$ , where  $|\phi\rangle_F$  is the state of the flag qubits. In summary, the RL agent must flag all harmful errors while preserving the logical state and keeping it disentangled from the flag qubits.

For the first criterion, we reward the agent based on the number of harmful errors that are flagged. We first apply circuit-level noise to the circuit U and obtain the set of all possible error operators  $\mathcal E$  in the circuit. When the agent applies a gate, which is faulty, we update the set  $\mathcal E$  by propagating errors from the applied gate and also the old errors. The set  $\mathcal E$  may grow with new errors or shrink because some errors may become obsolete.

At each time step t, we compute  $f_t$  (f for flag) given as,

$$f_t = \sum_{E \in \mathcal{E}} \begin{cases} 0 & \text{if } E \text{ is } I \text{ and a flag is triggered,} \\ 1 & \text{if } E \text{ is tolerable,} \\ 1 & \text{if } E \text{ is harmful and a flag is triggered,} \\ 0 & \text{if } E \text{ is harmful and flags are not triggered.} \end{cases}$$

(3)

The first term is used to prevent the agent from choosing a naive strategy like always flagging the ancilla (e.g. applying an X gate to the flag qubits).

We then normalize  $f_t$  by dividing it by the total number of errors  $|\mathcal{E}|$ . Note that some errors may initially have a large weight, but can be reduced by multiplication with a member of the stabilizer group. For instance, an error with weight 4 that is a member of the stabilizer group will have weight 0 and become a tolerable error. Therefore, to consider whether an error is tolerable or harmful, we compute the minimum weight of each error by multiplying it by all members of the stabilizer group when computing the reward. For instance, for the 5-qubit code, we check all  $2^5 = 32$  elements of the stabilizer group, including the state-dependent logical operator.

One might notice that if an error E is tolerable and the flag is triggered, the agent still gets a reward. This is inevitable, since it is not possible to both flag all of the harmful errors and with the same circuit construction unflag all of the tolerable errors. We can consider flagged tolerable errors as "unlucky" cases - note that this does not compromise FT, of course. One could add additional terms in the reward function to minimize this.

In principle, accurate FT circuit design requires consideration of every type of error that can occur in the circuit. However, CSS codes provide a further simplification in the design of fault-tolerant schemes. For instance, multiple Z errors usually lead to logical failures of the type  $Z_L|\Psi\rangle$  (assuming  $Z_L$  consists only of Z operators). Therefore, by restricting to  $|0\rangle_L$ , we make multiple Z errors tolerable, since  $Z_L|0\rangle_L=(+1)|0\rangle_L$ . Thus, only X and Y errors at the end of the encoding circuit are potentially harmful. The same applies to the preparation of  $X_L|+\rangle_L=|+\rangle_L$ , if  $X_L$  consists only of X operators, it is sufficient to consider Z and Y errors. Synthesis of FT encoding circuits for codewords  $|0\rangle_L$  and  $|+\rangle_L$  of CSS codes is then easier in the sense that either X or Z is not harmful by construction. However, this is not true for non-CSS codes, because the stabilizers have both X and Z Paulis, so the logical operators consist of both X and Z operators.

For the second criterion, we need to make sure that the circuit preserves the logical state  $|\psi\rangle_L$ . Here we can use the three possible functions discussed in Sec. IV. In this case, we reuse our proposed complementary tableau distance to measure the distance between the canonical tableau of the target logical state and the current error-free canonical tableau of the data qubits.

For the third criterion, we directly enforce the state to be a separable state of the data and ancilla flag qubits. This is necessary in order not to change the error-free logical state after the measurement of the ancilla qubits. In the stabilizer formalism, the latter is achieved by targeting the stabilizer generators of the ancilla in the current error-free canonical tableau to be Z in the location of the ancilla and I in the others. We can extract the canonical tableau of the ancilla qubits by taking the submatrix of the canonical tableau where the rows are n to  $n+n_A$ .

Therefore, we define a value  $p_t$  (p for product state) that measures the complementary tableau distance of the current error-free canonical tableau with the target tableau according to the above criteria. For an illustration of the reward calculation, see Appendix D.

We again use the reward shaping technique, which gives the reward function,

$$r_t = \mu_f(f_t - f_{t-1}) + \mu_d(d_{t-1} - d_t) + \mu_p(p_t - p_{t-1}),$$

(4)

where  $\mu$  defines the weight for each individual reward. A trajectory stops when all of the harmful errors are flagged, the prepared state is the logical state, and the data qubits and flag qubits are a product state (success) or the number of gates is greater than a threshold L (failure).

#### B. Results

Let us take non-FT state preparation circuits from the literature and use the RL method to synthesize the verification circuits. We then compare them with known verification circuits.

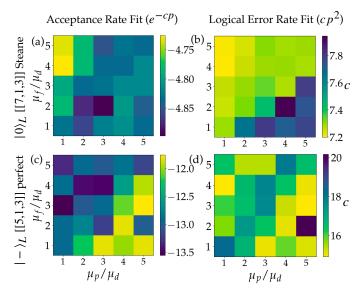

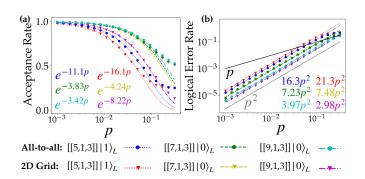

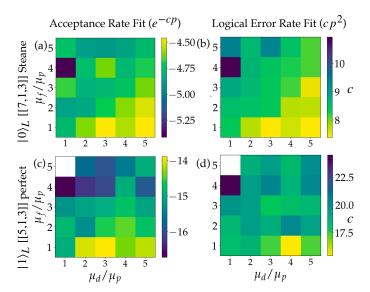

We use three metrics to compare different verification circuits. (i) First, we compare the number of two-qubit gates (one-qubit gates do not propagate errors) and the number of flag qubits. (ii) The second metric is the acceptance rate. A state outcome is accepted if, after running the circuit with noise, the flag qubits are not triggered. To determine the acceptance rate numerically, we simulate 10<sup>7</sup> noisy circuit trajectories for each varying error probability p by adding circuit-level noise using the STIM [121] library and count the number of accepted state outcomes. (iii) The final metric is the logical error rate  $p_L$ . When a state outcome is accepted, we perform a perfect round of error correction on the data qubits. We can then check if the decoded state is correct, otherwise, a logical error has occurred. As discussed in Sec. IIC,  $p_L$  of a fault-tolerant circuit should scale proportional to  $p^2$  for distance-3 codes, while it scales as p for non-faulttolerant circuits.

In our numerical experiments, we choose to use the standard gate set (H, S, and CNOT) combined with the CZ gate. The training of the agent starts with one flag qubit, and if the training does not converge, the number of flag qubits is incremented by one until a solution is found. We have also found empirically that prohibiting the agent from applying gates between the data qubits helps to speed up training convergence. In Appendix K, we show how different values of the weights  $\mu$  in the reward affect the acceptance and logical error rates.

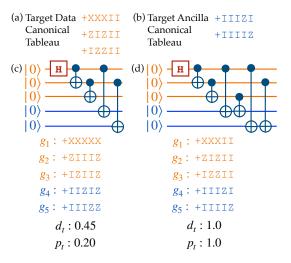

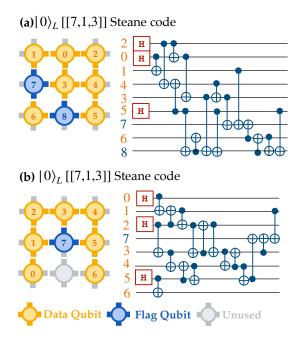

First, we synthesize the verification circuit for CSS codes. As discussed in Sec. II C, CSS codes have the favorable property that some errors are tolerable. We illustrate this by synthesizing the verification circuit for the  $|0\rangle_L$  preparation of the [[7,1,3]] Steane code with  $Z_L = Z^{\otimes 7}$ . The circuit was proposed in [32] (part of the

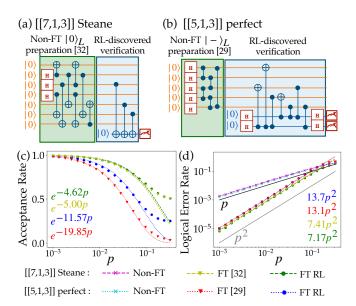

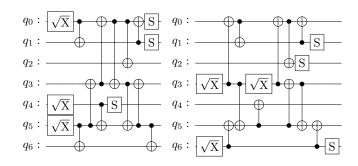

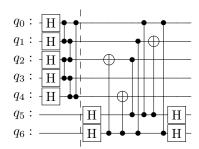

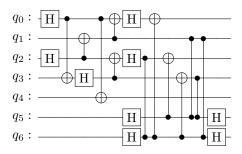

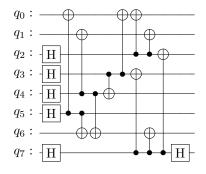

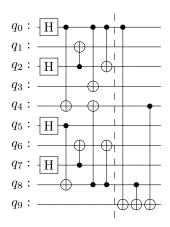

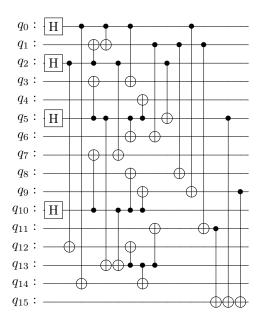

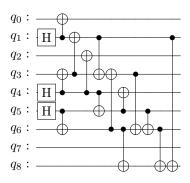

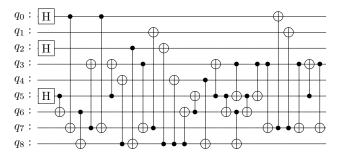

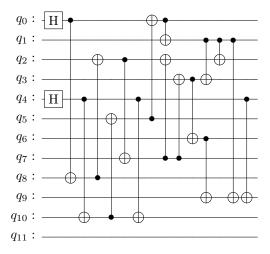

FIG. 6. Results for the verification circuit synthesis task. Examples of RL-discovered verification circuits (shaded in blue) for a given non-fault tolerant (FT) preparation (shaded in green) of (a) the  $|0\rangle_L$  state of the [[7,1,3]] Steane code from Ref. [32] and (b) the  $|-\rangle_L$  state of the [[5,1,3]] perfect code from Ref. [29]. In Ref. [32], the verification circuit uses 1 flag qubit and 3 two-qubit gates, which is the same as the circuit discovered by the RL agent. In Ref. [29], the verification circuit uses 6 flag qubits (or 2 flag qubits with 2 qubit resets) and 15 two-qubit gates, while the RL-discovered circuit in (b) uses only 2 flag qubits and 7 two-qubit gates. Comparison of the acceptance rate (c) and logical error rate (d) with different simulated error probability p for the circuits shown in (a) and (b) compared to non-FT circuits and circuits in [32] and [29].

circuit in Fig 6a shaded in green) and has been experimentally realized in [3, 6, 37, 38]. The RL agent discovers verification circuits with the same number of flag qubits and two-qubit gates as the one in [32]. Part of the circuit in Fig 6a, shaded in blue, shows an example of the verification circuit discovered by the RL agent. We show other discovered circuits in Appendix L. We observe that the RL agent learns to measure the stabilizer-equivalent logical Z operator IIZIZZI without being explicitly told. Although the discovered circuit has the same number of flag qubits and two-qubit gates, we see in Fig. 6(c),(d) that the acceptance rate and the logical error rate of the RL-discovered circuit are marginally better than the verification circuit proposed in [32].

We now move on to the synthesis of verification circuits for non-CSS codes. We choose to synthesize the verification circuit for the  $|-\rangle_L$  preparation of the [[5, 1, 3]] perfect code with  $X_L = XXXXX$  proposed in [29] and experimentally realized in [6, 7]. The blue-shaded part of the circuit in Fig 6b shows an example of the verification circuit discovered by RL. The RL agent learns to measure the stabilizer IIZXZ in the first ancilla and the stabilizer XIXZZ in the second ancilla. In Fig. 6(c),

we see that the RL-discovered circuit has a higher acceptance rate compared to the circuit in [29] due to the smaller circuit size and fewer flag qubits. Nevertheless, in Fig. 6(d), we see that the logical error rate is slightly worse than the circuit in [29]. However, the RL agent also discovers circuits with a lower logical error rate than the circuit in [29], at the expense of requiring 3 flag qubits. We show this circuit in Appendix L.

In this work, we consider only d=3 codes. The discovery of verification circuits for larger codes is challenging, but we could in principle extend our RL approach to higher distance codes. We illustrate the discussion with d=5 codes. In this case, the logical error rate  $p_L$  must be such that  $p_L \sim p^3$ , so that errors from two gate failures must be propagated. Therefore, we only need to change the way the error is propagated when training the RL agent. If L is the number of two-qubit gates, we need to propagate O(L) errors for d=3 and  $O(L^2)$  errors for d=5. In addition, L is also generally higher for d=5 codes than for d=3 codes. Our RL approach can be further improved by restricting the action space or by designing a better reward function, which we leave for future work.

In summary, we have shown that the RL method can be used to discover verification circuits for given non-FT logical state preparation circuits. We even show a case where the RL method discovers a better circuit than the existing circuit in the literature. Furthermore, interestingly the RL method can also discover variants of verification circuits with different tradeoffs in terms of logical error rates, acceptance rates, and the number of flag qubits.

## VI. INTEGRATED FAULT-TOLERANT LOGICAL STATE PREPARATION

### A. Task Description and Reward Function

FIG. 7. The integrated fault-tolerant logical state preparation task outputs a circuit W that directly prepares  $|\psi\rangle_L$  of a [[n, k, d]] code in a fault-tolerant way.

Individually, we have shown that RL methods are able to achieve competitive results for the tasks of logical state preparation and verification circuit synthesis. Here, we go beyond the separation of the tasks and present our main approach that integrates them to directly prepare logical states in a fault-tolerant manner.

We expect that this integration will allow the RL agent to devise a more effective strategy compared to separating the task for two main reasons. First, it will take error propagation into account when preparing the logical state. In addition, we expect the agent to perform better when preparing a fault-tolerant logical state under limited qubit connectivity. When we consider the two goals separately, instead, the RL agent does not take into account which data qubits are connected to the flag qubits when preparing the logical state.

The goal is to find a circuit W that prepares a logical state in a fault-tolerant way (see Fig. 7). The task requirement is the tableau of the target stabilizer state  $s_{target}$  and the number of available flag qubits  $n_A$ . Note that, with respect to the previous two tasks, it is possible though not necessary that the circuit W found by the RL agent is also decomposable into the state preparation circuit U and the verification circuit V.

The reward used for this task is the same as in Eq. (4). However, in this case, the RL agent starts from scratch, so the set of error operators  $\mathcal{E}$  is initially empty and grows as the agent performs actions by adding gates to the circuit construction attempt.

#### B. Results

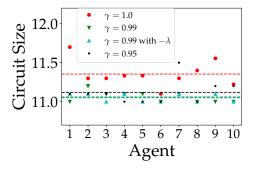

#### 1. All-to-all qubit connectivity

We first compare our two RL approaches to prepare a logical state in a fault-tolerant manner on all-to-all qubit connectivity. The first approach separates the task into logical state preparation (LSP) followed by verification circuit synthesis (VCS), which we refer to as LSP+VCS. The second one, instead, is our main approach that directly prepares the fault-tolerant logical state, which we refer to as integrated fault-tolerant logical state preparation (IFT-LSP).

We will discuss the preparation of the following logical states. For the CSS codes considered (i.e. the [[7,1,3]] Steane code, [[9,1,3]] Shor code, and [[15,1,3]] Reed-Muller code), we prepare the  $|0\rangle_L$  state with  $Z_L = Z^{\otimes n}$  and the  $|+\rangle_L$  state with  $X_L = X^{\otimes n}$ . For the non-CSS code (i.e. the [[5,1,3]] perfect code), we prepare the  $|1\rangle_L$  state with  $Z_L = ZZZZZ$  and the  $|-\rangle_L$  state with  $X_L = XXXXX$ . For this task, we also consider the [[9,1,3]] Surface-17 code [17], which has been realized experimentally, for example in [5, 8, 13].

In our numerical experiments, we again use the standard gate set combined with the CZ gate. The training of the agent starts with one flag qubit, and if the training does not converge, the number of flag qubits is incremented by one until a solution is found.

We compare the minimum number of two-qubit gates and the number of ancillas needed to prepare fault-tolerant logical states with the two RL approaches (LSP+VCS and IFT-LSP) and existing circuits in Table I. IFT-LSP is better than LSP+VCS at preparing

TABLE I. The comparison of fault-tolerant logical state preparation circuits on all-to-all qubit connectivity between our two RL approaches and existing circuits. We show the minimum number of two-qubit gates and the number of flag qubits in parentheses. Bold text indicates methods with the lowest number of two-qubit gates. The first RL approach is the LSP+VCS, where we separate the task by first performing the logical state preparation (LSP in Sec. IV) followed by the verification circuit synthesis (VCS in Sec. V). The second RL approach is our main approach, which is the integrated fault-tolerant logical state preparation (IFT-LSP in Sec. VI). We see that IFT-LSP always finds circuits with less or a similar number of two-qubit gates than LSP+VCS or existing circuits.

| Code                                    | State                          | LSP+VCS                 | IFT-LSP          | Existing                       |

|-----------------------------------------|--------------------------------|-------------------------|------------------|--------------------------------|

| [[5, 1, 3]]<br>perfect                  | $ 1\rangle_L$ $ -\rangle_L$    | 14 (2)<br>12 (2)        | 12 (2)<br>12 (2) | 20 (6) [29]                    |

| [[7, 1, 3]]                             | $ 0\rangle_L$                  | 11 (1)                  | 11 (1)           | 11 (1) [32]                    |

| Steane                                  | $ +\rangle_L$                  | 11 (1)                  | 11 (1)           |                                |

| [[9, 1, 3]]                             | $ 0\rangle_L$                  | 6 (0)                   | 6 (0)            |                                |

| Shor                                    | $ +\rangle_L$                  | 11 (1)                  | 11 (1)           |                                |

| [[9, 1, 3]]                             | $ 0\rangle_L$                  | 11 (1)                  | 11 (1)           | _a                             |

| Surface-17                              | $ +\rangle_L$                  | 11 (1)                  | 11 (1)           | -                              |

| $\frac{[[15,1,3]]}{\text{Reed-Muller}}$ | $ 0\rangle_L$<br>$ +\rangle_L$ | 29 (2)<br><b>31 (1)</b> | 25 (1)<br>31 (1) | <b>25 (1)</b> [34] 32 (1) [34] |

<sup>a</sup>Ref. [35] shows the FT preparation of  $|0\rangle_L$  state of the [[9,1,3]] surface-17 code with 8 two-qubit gates and 0 flag qubits. However, the connectivity of qubits is different, namely a  $3 \times 3$  grid without ancilla qubits. See also footnote [123].

two states:  $|1\rangle_L$  of [[5,1,3]] perfect code and  $|0\rangle_L$  of [[15,1,3]] Reed-Muller code. This is most likely because the LSP does not take error propagation into account when preparing the state. Compared to existing circuits in the literature, our RL approaches find a smaller number of two-qubit gates in two states:  $|-\rangle_L$  of [[5,1,3]] perfect code and  $|+\rangle_L$  of [[15,1,3]] Reed-Muller code. The first case is already shown in Fig. 6(b), while the second case needs one two-qubit gate less than the existing one. The circuits are shown in Appendix M. In terms of efficiency, both RL approaches are comparable. For example, to prepare the  $|0\rangle_L$  of the [[7,1,3]] Steane code, IFT-LSP needs about 150 seconds, while LSP+VCS needs about 180 seconds on a single NVIDIA Quadro RTX 6000 GPU.

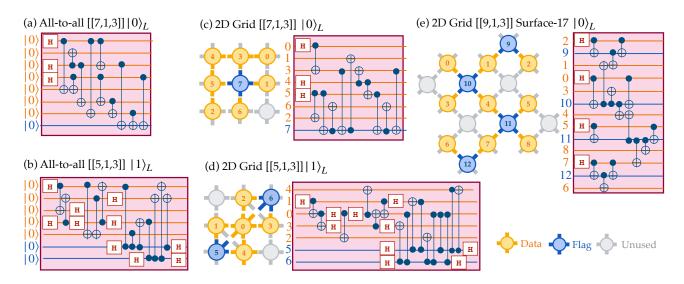

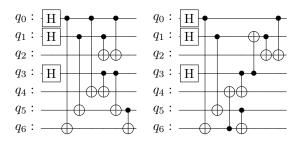

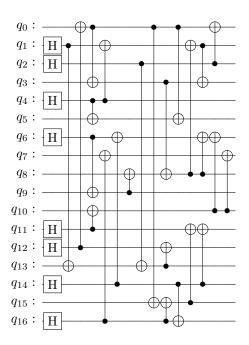

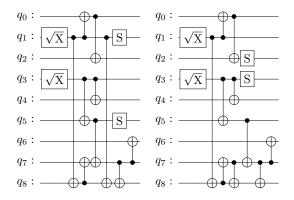

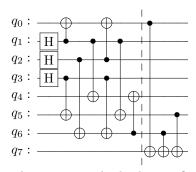

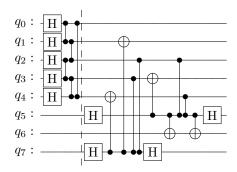

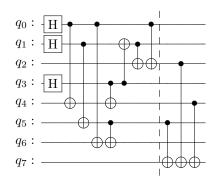

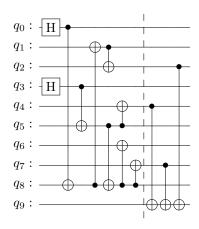

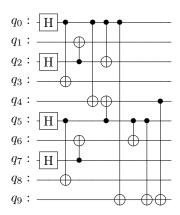

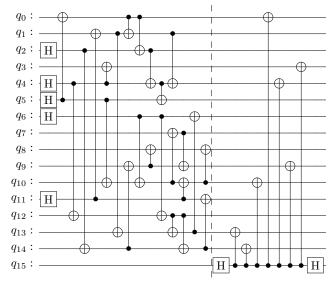

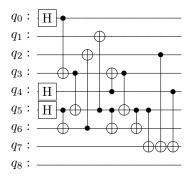

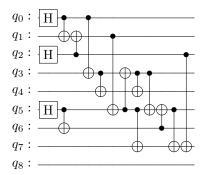

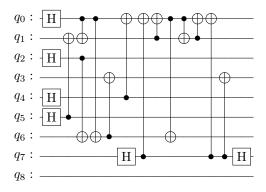

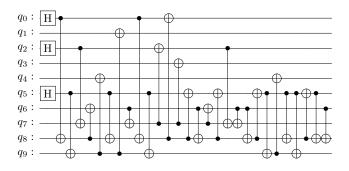

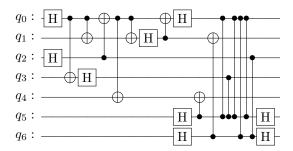

Fig. 8(a) and (b) show an example circuit for the fault-tolerant preparation of the  $|0\rangle_L$  state of the [[7,1,3]] Steane code and the  $|1\rangle_L$  state of the [[5,1,3]] perfect code discovered by IFT-LSP, respectively (see Appendix M for other examples of RL-discovered circuits). We can see that to prepare the  $|0\rangle_L$  state of the [[7,1,3]] Steane code, the RL agent measures the stabilizer-equivalent logical Z operator IIZZIIZ. When preparing the  $|1\rangle_L$  state of the [[5,1,3]] perfect code, the agent measures the stabilizer-equivalent logical Z oper-

FIG. 8. Results for the RL-based integrated fault-tolerant logical state preparation (IFT-LSP). An example of a fault-tolerant circuit prepared by an RL agent for (a) the  $|0\rangle_L$  state of the [[7,1,3]] Steane code and (b) the  $|1\rangle_L$  state of the [[5,1,3]] perfect code in all-to-all qubit connectivity. Parts (c) and (d) show learned fault-tolerant circuits for the same logical state preparation task on a 2D grid connectivity based on Google Sycamore [122] (c) and IBMQ Tokyo [116] (d) devices. In (e), we show, for the first time, flag-based fault-tolerant  $|0\rangle_L$  state preparation of the [[9,1,3]] Surface-17 code on a 2D grid connectivity and qubit placement taken from Refs. [5]. Note that the flag qubits (in blue) are measured, but for simplicity, the measurement is not shown. Unused qubits or connections (in gray) mean that they are available for use by the RL agent, but are not used in the solution found by the agent.

ator ZXIXZ via the first ancilla and XXIZI via the second ancilla.

As a side note, one can prepare other states by changing the logical operators. Alternatively, we can also apply logical gates to a prepared state. For example, it is known that the logical H gate in the [[7,1,3]] Steane code is transversal (applying H to each physical qubit), so it is still fault-tolerant. Thus, one can prepare  $|+\rangle_L$  by applying logical H to the prepared  $|0\rangle_L$ . However, this is not obvious for example in the [[5,1,3]] perfect code. In Ref. [6], the authors always prepare the  $|-\rangle_L$  fault-tolerantly first, and then rotate the logical basis state to another state. With our RL approach, instead, we can automatically discover fault-tolerant preparation circuits for other states.

### 2. Restricted qubit connectivity

We now move to a more general and practically relevant case where we show fault-tolerant logical state preparation on a device with restricted qubit connectivity. There are some handcrafted recipes for specific codes, such as encoding the  $|0\rangle_L$  state of the [[9,1,3]] surface-17 code in a 1D array [35] and encoding a magic state of the [[4,1,2]] code in an IBMQ device [124]. Here, we want to use RL instead to automatically discover such circuits.

Note that transpiling a fault-tolerant circuit prepared for all-to-all qubit connectivity generally does not work, since it does not guarantee that the transpiled circuit is fault-tolerant. Additionally, we find that separating the task (LSP+VCS) fails in some cases. The first case is when a data qubit is connected only to the ancillas. In this scenario, one would have to use the ancilla as a "bridge" to the corresponding data qubit. The second case is when the VCS fails because the LSP does not take the position of the ancilla into account when preparing the logical state. In contrast, our main approach (IFT-LSP) works in these conditions. We discuss these two cases in more detail and give examples in Appendix N.

We illustrate our main approach by preparing faulttolerant logical states on a 2D grid, which is common in quantum chips based on superconducting qubits (e.g. Google Sycamore [122], IBM Quantum devices, Rigetti Ankaa). We first demonstrate the fault-tolerant preparation of the  $|0\rangle_L$  for the [[7, 1, 3]] Steane code on a  $3\times3$  grid based on the Google Sycamore device. Fig. 8(c) shows an example of an RL-discovered circuit. Impressively, the RL agent discovers a circuit with the same number of two-qubit gates and flag qubits as in the all-to-all qubit connectivity shown in Fig. 8(a). Fig. 8(d) shows an example of the fault-tolerant preparation of the  $|1\rangle_L$  for the [[5,1,3]] perfect code on a 2D grid based on the IBMQ Tokyo [116] device. Compared to the circuit on all-to-all qubit connectivity, it has the same number of flag qubits and requires only 4 additional two-qubit gates. The RL approach also manages to discover circuits for the preparation of other logical states, including for the [[9, 1, 3]] Shor code, which we show in Appendix P.

The logical state of a surface code is commonly prepared fault-tolerantly by using repeated stabilizer measurements [125, 126]. Here, we for the first time show RL-

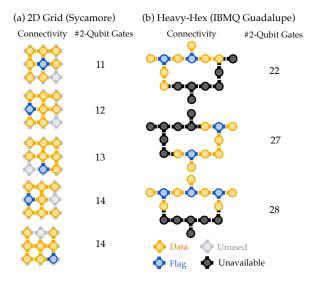

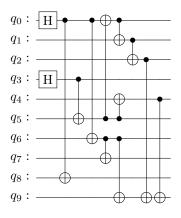

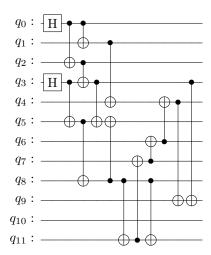

FIG. 9. Exploration of different qubit connectivity and placement for the integrated fault-tolerant  $|0\rangle_L$  state preparation of the [[7,1,3]] Steane code. We show the number of two-qubit gates in some of the RL-discovered circuits with (a) 2D grid (based on the Google Sycamore device) and (b) heavy-hex layout (based on the IBMQ Guadalupe [115] device). Unused qubits and connectivities (in gray) mean that the qubits were given to the RL agent to be used as flag qubits, but were not used. Unavailable qubits and connectivities (in black) mean that the qubits are not set as available to the RL agent.

discovered flag-based fault-tolerant logical state preparation of a surface code in the standard 2D grid connectivity: We illustrate this by preparing the  $|0\rangle_L$  of the [[9,1,3]] Surface-17 code with the connectivity and qubit placement from [5] in Fig. 8(e). The repeated stabilizer measurements preparation needs 8 syndrome qubits, while RL-discovered circuit, although given 8 flag qubits to use, only needs 4 flag qubits and uses 16 two qubit gates. It is only 5 two-qubit gates more than preparing it in an all-to-all qubit connectivity as shown in Table I (the circuit is shown in Appendix M) [123]. The discovered circuit shows a novel approach to fault-tolerantly prepare a logical Pauli state of the surface code.

In Appendix O, we compare the logical error and acceptance rates of the circuits shown in Fig. 8. In all cases the logical error rate scales as  $p^2$ , confirming that the circuits are fault-tolerant, as desired. In Appendix Q, we show how different values of the weight  $\mu$  in the reward affect the acceptance and logical error rates.

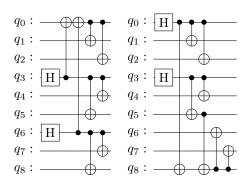

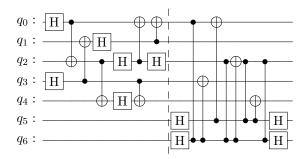

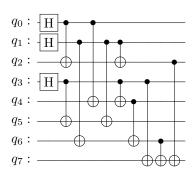

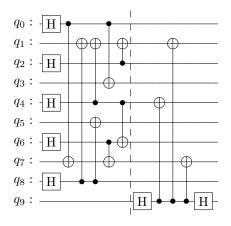

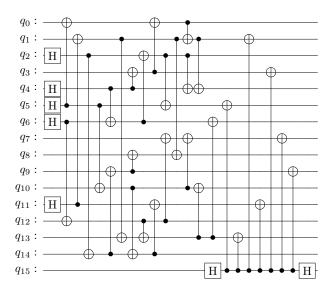

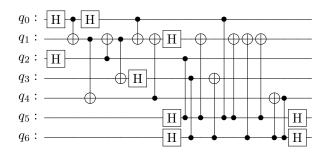

We now show that the RL approach allows a straightforward exploration of different qubit connectivity and placements, i.e., assignments of data and flag qubits to physical qubits of the underlying device, by training different RL agents. We illustrate this by preparing the  $|0\rangle_L$  state for the [[7,1,3]] Steane code. On a  $3\times 3$  grid based on the Google Sycamore device, there are  $\binom{9}{7}=36$  possible data and flag qubit placements. We train on all possible configurations and in Fig. 9(a), we show 5 qubit placements where the circuit discovered by the RL agent

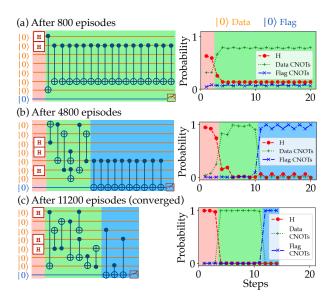

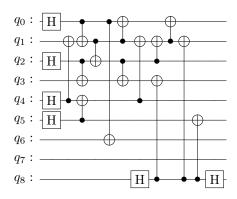

FIG. 10. Evolution of the learned strategy during training. We train an RL agent for the integrated fault-tolerant  $|0\rangle_L$ state preparation of the [[7, 1, 3]] Steane code, assuming allto-all qubit connectivity. The left part of the figure shows the circuit prepared by the agent. The right part shows the probability of actions for each step. We group the actions into 3main groups: applying Hadamard gates on some qubits (red), applying CNOTs between data qubits (green), and applying CNOTs between data qubits and flag qubits (blue). The background color indicates the most probable group of actions at that step. We can see the progression of the RL agent's learning process, starting from applying mostly Hadamard gates in the first few steps in (a), followed by learning how to prepare the logical state in (b), and finally learning how to prepare the state and flag the harmful errors after convergence in (c). We hypothesize that the agent applies long sequences of self-cancelling CNOTs in (a) and (b) because it has not yet learned what to do in the later time steps. The agent then chose a "safe" strategy by applying multiple CNOTs several times, which does not change the reward.

has the lowest number of two-qubit gates. Next, we illustrate the same preparation for heavy-hex connectivity based on the IBMQ Guadalupe device. We show 3 data and flag qubit placements where the circuit has the lowest number of two-qubit gates in Fig. 9(b). We have also tried different flag qubit placements, but sometimes the agent does not find an encoding circuit, especially when the flag qubit is not located in the crossing (i.e. the flag qubit is connected to 3 data qubits). This may indicate that the best flag qubit placement in the heavy-hex connectivity is in the crossings. We provide the circuits in Appendix P.

One might expect that when the RL agent directly prepares a fault-tolerant logical state, it would try to detect some harmful errors in the middle of the preparation. This is indeed the case, for example, in the circuit shown in Fig. 8(c). However, we observe that most of the discovered circuits can be decomposed into a state preparation circuit U, followed by a verification circuit V (e.g., the

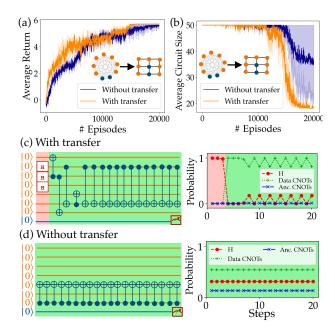

FIG. 11. Transfer learning for integrated fault-tolerant logical state preparation from an all-to-all qubit connectivity to a 2D grid connectivity. Part (a) shows the average return and (b) shows the circuit size during training for the fault-tolerant  $|0\rangle_L$  preparation of the [[7, 1, 3]] Steam code with and without transfer learning. The training without transfer learning also converges, but requires more training. The central part (c) shows that when we directly use the transferred agent without training, the agent retains the knowledge of placing Hadamard gates as shown previously in Fig. 10. This is in contrast to the case without transfer learning shown in (d), where the agent applies only a long sequence of self-cancelling CNOTs. In this case, the agent has not learned anything, so the probability of each gate is still uniform. The CNOT gate between qubit 7 and 5 is just a random gate chosen by the agent.

circuits shown in Fig. 8(a), (b), and (d)).

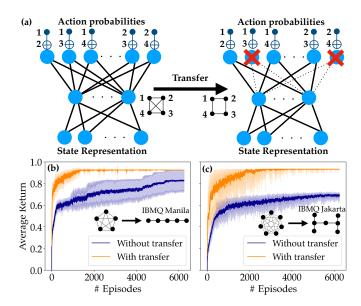

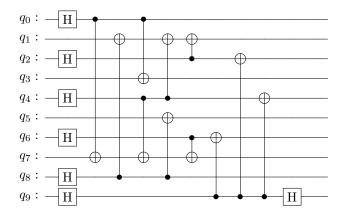

We can try to investigate the strategy that the RL agent learns by looking at the circuits and the action probabilities during the training. We illustrate this in Fig. 10. We see that in the initial training steps, the agent applies Hadamard gates to initialize some qubits in the  $|+\rangle$ , which is a known strategy for CSS codes [83]. Next, the agent learns to prepare the logical state circuit without flagging harmful errors. Finally, the agent learns to flag the harmful errors until the training converges. We illustrate this strategy for the integrated fault-tolerant preparation of the  $|0\rangle_L$  state of the [[7,1,3]] Steane code on all-to-all qubit connectivity in Fig. 10.

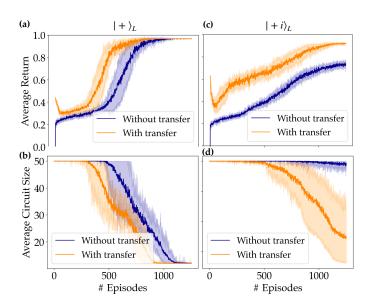

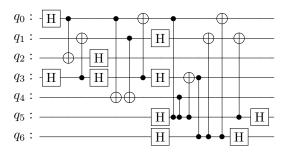

Finally, we want to explore the possibility of transfer learning in this task. Transfer learning is a powerful technique in machine learning that leverages knowledge or a strategy gained from solving one problem to solve related but different problems. However, transfer learning does not always work effectively because it depends heavily on the similarity of the problems [119].

We show a transfer learning technique where we reuse

the agent that was trained to prepare a fault-tolerant logical state in an all-to-all qubit connectivity scenario to prepare the same state for the situation of restricted connectivity. The transfer learning process is explained in detail in Appendix J. We find that transfer learning helps to make the training converge faster. Additionally, we see that the transferred agent retains the strategy from the previous training. We illustrate this by comparing the integrated fault-tolerant preparation of the  $|0\rangle_L$  state of the [[7,1,3]] Steane code on a 2D grid without and with transfer learning from all-to-all qubit connectivity in Fig. 11.

In summary, we have shown that the integrated fault-tolerant logical state preparation (IFT-LSP) approach always finds circuits with better or similar performance, both compared to circuits known in the literature as well as compared to circuits found by separating the task into the two subtasks (LSP+VCS). We have also demonstrated state-of-the-art RL-based fault-tolerant logical state preparation for restricted qubit connectivity scenarios with different connectivity and qubit placements. Furthermore, with transfer learning, we can reuse an RL agent trained for all-to-all qubit connectivity to accelerate the training for restricted qubit connectivity.

## VII. CONCLUSIONS AND OUTLOOK

We have presented reinforcement learning (RL) approaches to discover quantum circuits for fault-tolerant (FT) logical state preparation of QEC codes based on flag qubit protocols. We have started with the non-FT logical state preparation task and showed that RL prepares the logical state with a smaller circuit size than other methods for the all-to-all qubit connectivity scenarios. We have also highlighted that including the hardware constraint directly in the training yields quantum circuits with a smaller circuit size than transpiling a circuit for all-to-all qubit connectivity. We have then synthe sized verification circuits to perform FT logical state preparation. We have demonstrated that RL can discover verification circuits that perform better than or equal to existing circuits in the literature. We have shown that the main approach that we advocate in this work, where we integrate the subtasks into the challenge of direct integrated fault-tolerant logical state preparation (IFT-LSP), performs even better than separating the tasks. Furthermore, we have demonstrated RL-based fault-tolerant logical state preparation under constrained connectivity for different qubit connectivity and placements. Finally, we have investigated and shown that transfer learning can help speed up the training process of the RL agent.

In this work, we have demonstrated the first steps in using an RL approach for the automatic discovery of quantum circuits for fault-tolerant protocols in quantum error correction. Our approach could naturally be extended and applied to different tasks, such as the dis-

covery of quantum circuits for fault-tolerant magic state preparation [36, 69], syndrome measurement [127, 128], logical gates, error correction cycles, and other quantum error correction subroutines. On the one hand, exploring these scenarios will not require a completely different approach, since verification-like circuits can be used to render the tasks fault-tolerant. However, such extensions will require a careful design of the appropriate reward function, set of actions, and observations to effectively train the RL agent. It will also be interesting to explore several avenues for scalability: on the one hand, this could include for instance devising modular formulations of the FT compilation tasks, e.g., by including more complex building blocks, such as sub-circuits for specific tasks such as stabilizer readout, in the set of actions available to the RL agent. On the other hand, it would be exciting to explore the potential of collaborative multi-agent RL scenarios, which may allow one to apply the techniques proposed in this work to larger-distance and concatenated error correction codes.

Fuente, and Manuel Rispler for fruitful discussions. The research is part of the Munich Quantum Valley (K-4 and K-8), which is supported by the Bavarian state government with funds from the Hightech Agenda Bayern Plus. L.C. and M.M. furthermore acknowledge support by the US Army Research Office through Grant Number W911NF-21-1-0007. M.M. also acknowledges support by the European Union's Horizon Europe research and innovation program under Grant Agreement Number 101114305 ("MILLENION-SGA1" EU Project), the ERC Starting Grant QNets through Grant Number 804247, and by the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation) under Germany's Excellence Strategy 'Cluster of Excellence Matter and Light for Quantum Computing (ML4Q) EXC 2004/13 390534769.

### ACKNOWLEDGMENTS

We thank Sangkha Borah, Maximilian Nägele, Oleg Yevtushenko, Josias Old, Julio Carlos Magdalena de la

[1] J. Preskill, Quantum Computing in the NISQ era and beyond, Quantum 2, 79 (2018), arXiv:1801.00862 [condmat, physics:quant-ph].

<sup>[2]</sup> D. Gottesman, An introduction to quantum error correction and fault-tolerant quantum computation, in *Proceedings of Symposia in Applied Mathematics*, Vol. 68, edited by S. Lomonaco (American Mathematical Society, Providence, Rhode Island, 2010) pp. 13–58.

<sup>[3]</sup> L. Postler, S. Heußen, I. Pogorelov, M. Rispler, T. Feldker, M. Meth, C. D. Marciniak, R. Stricker, M. Ringbauer, R. Blatt, P. Schindler, M. Müller, and T. Monz, Demonstration of fault-tolerant universal quantum gate operations, Nature 605, 675 (2022).

<sup>[4]</sup> I. Cong, H. Levine, A. Keesling, D. Bluvstein, S.-T. Wang, and M. D. Lukin, Hardware-Efficient, Fault-Tolerant Quantum Computation with Rydberg Atoms, Phys. Rev. X 12, 021049 (2022).